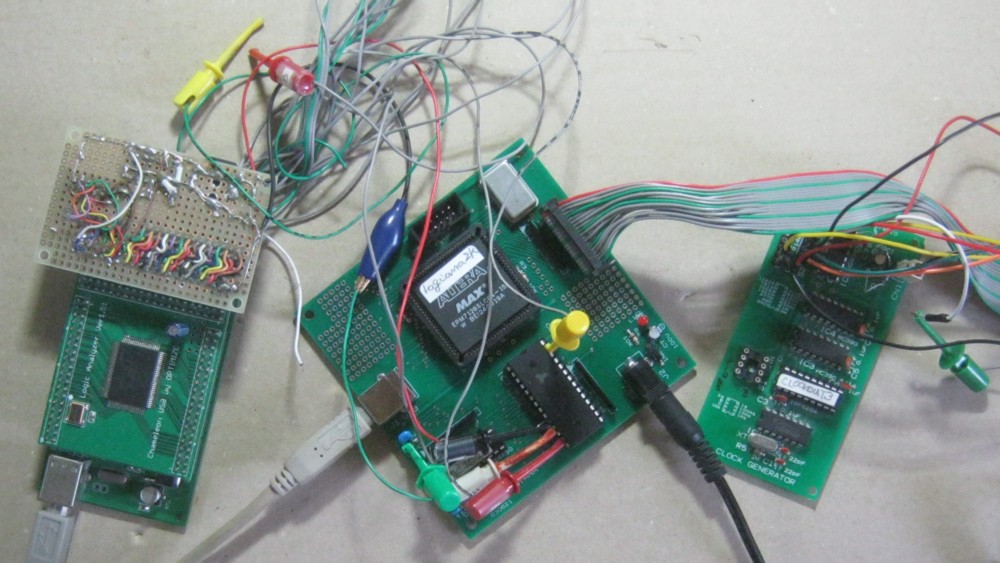

仠俠俹俴俢儘僕傾僫乮俋乯俀俆俵俫倸偱僥僗僩乮侾乯

慜夞偼俠俹俴俢儘僕傾僫偵幚憰梊掕偺俙俽俇俠俇俀俀俆俇偺傾僋僙僗僞僀儉傪妋擣偟偨偲偙傠僒儞僾儕儞僌僋儘僢僋俀侽俵俫倸偵懳偟偰偼傢偢偐偱偡偑僗儁僢僋偑崌傢側偄偙偲偑傢偐傝傑偟偨丅

偟偐偟幚嵺偺摦嶌妋擣偱偼俀侽俵俫倸偱傕栤戣側偔摦嶌偟偰偄傑偡丅

僨乕僞僔乕僩偵傛傞偲俙俽俇俠俇俀俀俆俇偼俀丏俈倁乣俆丏俆倁偺峀偄揹埑斖埻偱摦嶌偟傑偡丅

僨乕僞僔乕僩偺抣偼倁們們亖俁倁傪婎弨偵偟偰偄傞偲傕峫偊傜傟傞偺偱丄偦傟側傜偽倁們們亖俆倁偱偺摦嶌側傜偽僨乕僞僔乕僩偺傾僋僙僗僞僀儉傛傝傕崅懍偱傾僋僙僗偱偒傞偼偢偲峫偊傜傟傑偡丅

偟偐偟偦傟偼偦偺傛偆偵悇應偟偰偄傞偩偗偱偼偭偒傝偟偨崻嫆偑偁偭偰偺偙偲偱偼偁傝傑偣傫丅

偱偡偺偱慜夞偼丄俀侽俵俫倸偼乽偍傑偗乿偲峫偊偰偔偩偝偄丄偲彂偒傑偟偨丅

傂傚偭偲偡傞偲俀侽俵俫倸偼偨傑偨傑摦嶌偟偰偄傞偩偗偱丄惓偟偔摦偐側偄応崌傕偁傞偐傕偟傟側偄丄偲傕巚偭偨偐傜偱偡丅

偟偐偟丅

堦斢宱偪傑偡偲偦偺傑傑偵偟偰偍偔偺偼偳偆偵傕婥帩偪偑埆偄偲巚偆傛偆偵側偭偰偒傑偟偨丅

側偐側偐偵崲偭偨惈暘偱偁傝傑偡丅

偼偭偒傝偟偨崻嫆偑側偄側傜孞傝曉偟僥僗僩傪偡傞側偳偟偰妋幚偵摦嶌偡傞偙偲傪妋偐傔傟偽偦傟偼偦傟偱傂偲偮偺崻嫆偲偟偰帵偡偙偲偑偱偒傞偲巚偄傑偡丅

傕偭偲傛偄曽朄偼俀侽俵俫倸傛傝傕崅偄僋儘僢僋偱摦嶌妋擣傪偟偰傒傞偙偲偱偡丅

偮傑傝尷奅傪妋擣偟偰傒傞偙偲偱丄偦傟傛傝傕掅偄廃攇悢側傜戝忎晇偲偄偆埨怱傪摼傞偙偲偑偱偒傑偡丅

偨偲偊偽俀俆俵俫倸偲偐偱帋偟偰傒偨傜偳偆偐側傫偰偙偲傪巚偄偮偄偰偟傑偄傑偟偨丅

傑丅

懡暘岆摦嶌偡傞偱偟傚偆偗傟偳丅

傗偭偰傒側偗傟偽傢偐傝傑偣傫丅

巚偄偮偄偨傜傗偭偰傒傞偙偲偱偡丅

偲偄偆偙偲偱丄偲偵偐偔懯栚尦偱俀俆俵俫倸偱帋偟偰傒傞偙偲偵偟傑偟偨丅

俀俆俵俫倸偺応崌偼壓偺攇宍恾偺傛偆偵側傝傑偡丅

俵俤俵倂俼怣崋偼們値倲倰俴偺價僢僩侽偲價僢僩侾偺俙俶俢偐傜嶌傝傑偡丅

俙俽俇俠俇俀俀俆俇偺僨乕僞僔乕僩偱偺抣偱偼倂俼俬俿俤僷儖僗偺僒僀僋儖僞僀儉偺嵟彫抣偼俆俆値倱偱俴婜娫偺暆偺嵟彫抣偼係俆値倱偱偡丅

僨乕僞僔乕僩偺嵟彫抣傛傝傕侾俆値倱傕彫偝偄偱偡傕偺偹丅

偙傟偼傗傞慜偐傜柍棟偲偄偆傕偺丅

偱傕偙偙傑偱偒偨傜傗傞偟偐側偄偱偟傚偆丅

壓偼偦偺晹暘偺倁俫俢俴僾儘僌儔儉偱偡丅