乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣

偄偮偐巊偆偙偲偵側傞偩傠偆偲巚偭偰偼偄偨偺偱偡偑丅

壗傪崱崰偵側偭偰丄偲偄偆傛偆側傕偺偱偡偑丅

傛偆傗偔杮婥偱丄俠俹俴俢偲巐偮偵庢傝慻傒傑偡丅

乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣

乵戞侾俀夞乶

仠俹倝値丂俹倢倎値値倕倰

崱夞偼夞楬偺婰弎偵偮偄偰彂偔梊掕偱偟偨偑丄梊掕曄峏偱偡丅

慜夞偼倁俫俢俴僾儘僌儔儉偱擖弌椡抂巕乮偺怣崋柤乯傪掕媊偟傑偟偨丅

摉慠偦偺擖弌椡怣崋抂巕偼俠俹俴俢偺偳偙偐偺抂巕偵寢傃晅偗側偗傟偽側傝傑偣傫丅

偄偢傟傑偨徻偟偔愢柧偡傞偙偲偵側傞偲巚偄傑偡偑丄愢柧偺棳傟偲偟偰丄偙偺偁偨傝偱偦偺偙偲偵偮偄偰娙扨偵彂偄偰偍偔偙偲偵偟傑偡丅

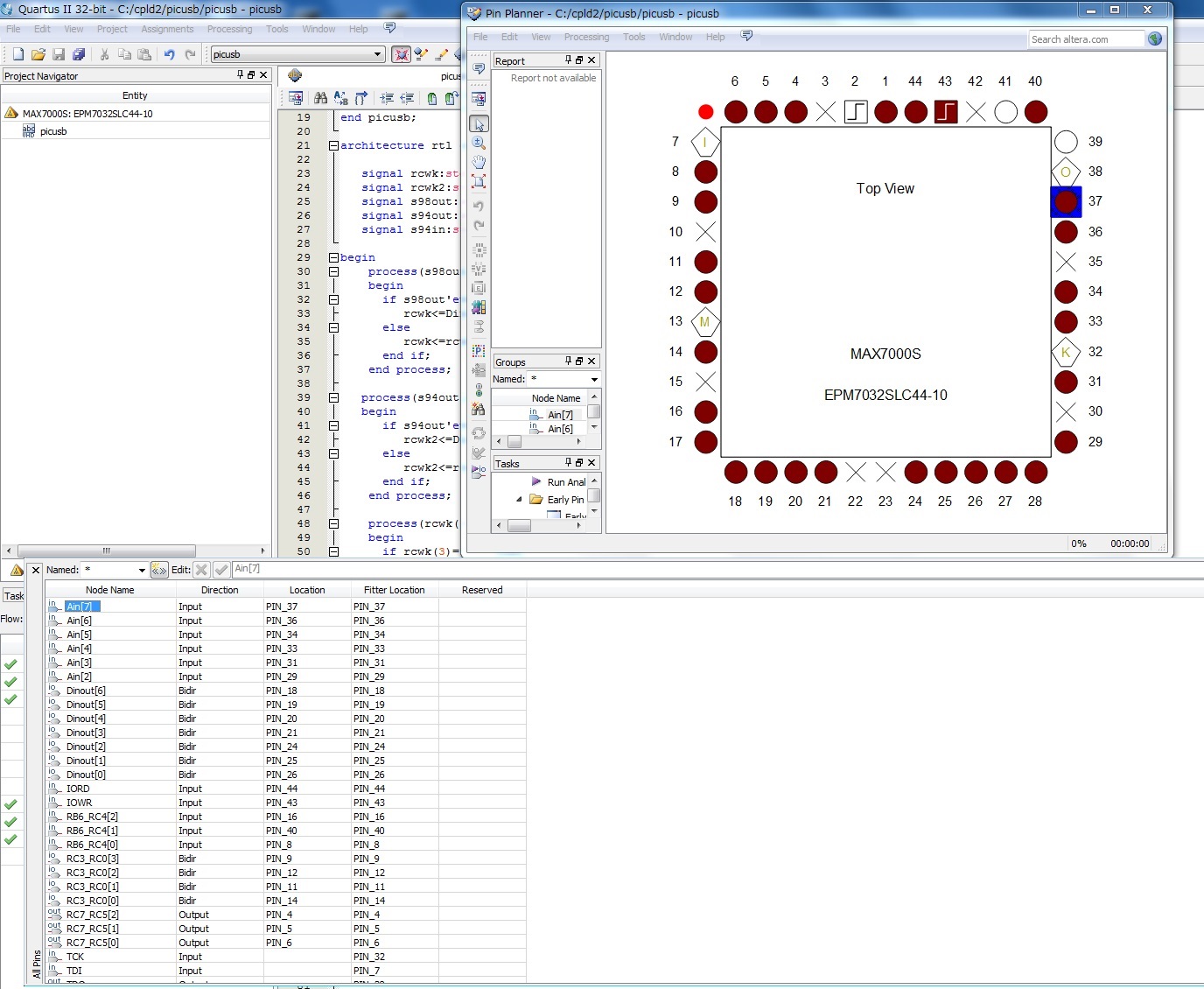

倃俬俴俬俶倃偺俬俽俤丂俢倕倱倝倗値丂俽倳倝倲倕偱偼丄倁俫俢俴偱愝掕偟偨奜晹抂巕傪俠俹俴俢偺幚嵺偺抂巕斣崋偵寢傃偮偗傞乮僺儞傾僒僀儞乯偨傔偵丄俹俬俶丵俙俽俽俬俧俶傪巊偄傑偡乮乽俠俹俴俢亄俽俬俵俵傪巊偭偰倀俽俛僾儘僩僐儖偺夝愅傪両乿乵戞俉係夞乶偺儕僗僩傪嶲徠乯丅

偙傟偵懳偟偰俙俴俿俤俼俙偺俻倀俙俼俿倀俽嘦偱偼丄倁俫俢俴僾儘僌儔儉撪偱偼僺儞傾僒僀儞偼婰弎偟傑偣傫丅

俻倀俙俼俿倀俽嘦偺拞偺俹倝値丂俹倢倎値値倕倰偲偄偆僣乕儖傪巊偄傑偡丅

俹倝値丂俹倢倎値値倕倰偺巊偄曽偵偮偄偰偼偄偢傟徻偟偔愢柧偟傑偡偑丄俹倝値丂俹倢倎値値倕倰傪幚峴偡傞偲忋偺傛偆側夋柺偵側傝傑偡丅

夋柺忋晹偵偼俠俹俴俢偺抂巕恾偑昞帵偝傟傑偡丅

嵍壓偵偼倁俫俢俴僾儘僌儔儉偱掕媊偟偨奜晹抂巕柤偲俠俹俴俢偺僺儞斣崋偺愙懕昞偑昞帵偝傟傑偡丅

俹倝値丂俹倢倎値値倕倰傪嵟弶偵幚峴偡傞偲丄俹倝値丂俹倢倎値値倕倰偑彑庤偵寢傃偮偗偨昞偑昞帵偝傟傑偡丅

暿偺抂巕偵妱傝摉偰偨偄偲偒偼昞偺抂巕柤乮俶倧倓倕丂俶倎倣倕乯傪儅僂僗偱巜掕偟偰偦偺傑傑夋柺忋晹偺妱傝摉偰偨偄抂巕斣崋偺偲偙傠偵傕偭偰峴偭偰偦偙偱棊偲偡偲丄偦傟偑昞偵斀塮偝傟傑偡丅

偙偺曽朄偼帇妎揑偱丄偆偭偐傝栚揑偲偼堘偆抂巕偵妱傝摉偰偰偟傑偆偲偄偆娫堘偄傪杊偖偙偲偑偱偒傞偲偄偆挿強偑偁傝傑偡丅

偟偐偟僺儞悢偺彮側偄俠俹俴俢偺応崌偵偼傛偄偺偱偡偗傟偳僺儞悢偑懡偄俠俹俴俢偵側偭偰偔傞偲丄側偐側偐偵崪偺愜傟傞嶌嬈偵側傝傑偡丅

倃俬俴俬俶倃偺俬俽俤丂俢倕倱倝倗値丂俽倳倝倲倕偺応崌偺傛偆偵僥僉僗僩偲偟偰掕媊偡傞偙偲偱丄偦傟傪悧宍偲偟偰暿偺倁俫俢俴僾儘僌儔儉傪彂偔偲偒偵偦傟傪僐僺乕偟偰揬傝晅偗偰偍偄偰丄偦偙偱庤捈偟偡傞偲偄偆傗傝曽偺曽偑曋棙偐側偁偲巚偊傞偲偙傠傕偁傝傑偡丅

傑偁偳偪傜傕偦傟偧傟挿抁偑偁傞傛偆偵傕巚偊傑偡丅

僱僢僩傪専嶕偟偰挷傋偰傒偨偲偙傠俙俴俿俤俼俙偺俻倀俙俼俿倀俽嘦偱傕抂巕偺寢傃晅偗傪僥僉僗僩僼傽僀儖偱峴側偆曽朄傕偁傞偙偲偑傢偐傝傑偟偨丅

偪傚偭偲棤儚僓揑側偺偱偡偗傟偳丅

偦傟偵偮偄偰傕偄偢傟彂偔偙偲偵偄偨偟傑偡丅

埲忋崱夞偼慜夞偺曗懌愢柧偱偟偨丅

師夞偼夞楬偺婰弎偵偮偄偰彂偒傑偡丅

俠俹俴俢擖栧両乵戞侾俀夞乶

俀侽侾俋丏俀丏俀俆倳倫倢倧倎倓

慜傊

師傊

儂乕儉儁乕僕僩僢僾傊栠傞