[新連載]CPLD入門!

〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜

いつか使うことになるだろうと思ってはいたのですが。

何を今頃になって、というようなものですが。

ようやく本気で、CPLDと四つに取り組みます。

〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜

[第49回]

●VHDLプログラムリスト

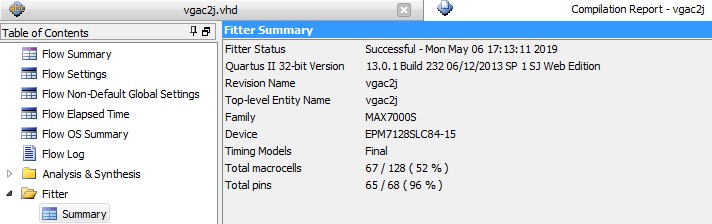

CPLD版VGAIFのVHDLプログラムです。

--vga controller 18/12/22 12/23 12/24 12/25 12/26 12/27

--19/1/12 1/13 1/29 3/24 3/25 3/26 3/27

--5/4 5/5 5/6

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

library ARITHMETIC;

use ARITHMETIC.std_logic_arith.all;

entity vgac2j is

PORT (

AHout:out std_logic_vector(6 downto 0);

ALout:out std_logic_vector(3 downto 0);

AHin:in std_logic_vector(6 downto 0);

ALin:in std_logic_vector(3 downto 0);

ROMadrs:out std_logic_vector(2 downto 0);

ROMDATA:in std_logic_vector(7 downto 0);

A11_15:in std_logic_vector(4 downto 0);

IOWR:in std_logic;

IORD:in std_logic;

MREQ:in std_logic;

MWR:in std_logic;

VRAMWR:out std_logic;

VRAMS:out std_logic;

D0IN:in std_logic;

D1IN:in std_logic;

D7OUT:out std_logic;

RGB_ROUT:out std_logic;

RGB_GOUT:out std_logic;

RGB_BOUT:out std_logic;

HSYNC :out std_logic;

VSYNC :out std_logic;

Notused58:in std_logic;

Notused73:in std_logic;

Notused74:in std_logic;

T57:out std_logic;--vblnkwk

T67:out std_logic;--vactive

T68:out std_logic;--hblnkwk

T69:out std_logic;--hblnkwk2

Resetin:in std_logic;

CKIN :in std_logic);

end vgac2j;

architecture rtl of vgac2j is

signal cntr1:std_logic_vector(2 downto 0);

signal cntr2:std_logic_vector(6 downto 0);

signal cntr3:std_logic_vector(8 downto 0);

signal ramadrswk:std_logic_vector(6 downto 0);

signal ramadrswk0:std_logic_vector(6 downto 0);

signal sftrgstr:std_logic_vector(7 downto 0);

signal hblnkwk:std_logic;

signal hblnkwk2:std_logic;

signal cntr3wk:std_logic;

signal vblnkwk:std_logic;

signal vrams2:std_logic;

signal vactive:std_logic;

signal rgbout:std_logic;

signal hsyncwk:std_logic;

signal vsyncwk:std_logic;

begin

T57<=vblnkwk;

T67<=vactive;

T68<=hblnkwk;

T69<=hblnkwk2;

Hsync<=hsyncwk;

Vsync<=vsyncwk;

--cntr1 & sftrgstr

process(CKIN)

begin

if CKIN'event and CKIN = '1' then

cntr1<=cntr1+"001";

sftrgstr<=sftrgstr(6 downto 0) & '0';

end if;

if CKIN='1' and cntr1="111" then

sftrgstr<=ROMDATA;

end if;

end process;

--cntr2

process(cntr1)

begin

if cntr1(2)'event and cntr1(2) = '0' then

cntr2 <= cntr2 +"0000001";

end if;

if cntr2="1100100" then

cntr2<="0000000";

end if;

end process;

--hblnk,hsync

process(cntr2)

begin

--hblnkwk

if cntr2="0000000" then

hblnkwk<='1';

--elsif cntr2="0000001" then see note 5/6

hblnkwk2<='1';

elsif cntr2="1010000" then

hblnkwk<='0';

elsif cntr2="1010001" then

hblnkwk2<='0';

--hsynkwk

elsif cntr2="1010011" then

hsyncwk<='0';

elsif cntr2="1011111" then

hsyncwk<='1';

end if;

end process;

--cntr3

process(hblnkwk)

begin

if hblnkwk'event and hblnkwk = '1' then

cntr3 <= cntr3 +"000000001";

end if;

if cntr3="111000001" then

cntr3<="000000000";

end if;

end process;

-- vblnk,vsync

process(cntr3)

begin

--vblnkwk

if cntr3(8)='0' then

vblnkwk<='1';

elsif cntr3(8 downto 4)="11001" then

vblnkwk<='0';

end if;

--vsyncwk

if cntr3="110011100" then

vsyncwk<='0';

elsif cntr3="110011110" then

vsyncwk<='1';

end if;

end process;

--ramadrs

process(cntr2,cntr3,vblnkwk)

begin

if vblnkwk='0' then

ramadrswk<="0000000";

ramadrswk0<="0000000";

elsif cntr3(3 downto 0)="1111" and hblnkwk = '0' then

ramadrswk0 <= ramadrswk;

elsif cntr2="1010000" and cntr1(0)='1' then

ramadrswk <= ramadrswk0;

elsif cntr2(3)'event and cntr2(3)='0' and hblnkwk='1' then

ramadrswk<=ramadrswk+"0000001";

end if;

end process;

-- address select

-- vrams

process(MREQ,MWR)

begin

if MREQ='0' and MWR='0' and A11_15="11111" and vrams2='0' then

VRAMS<='0';

AHout<=AHin;

ALout<=ALin;

VRAMWR<=MWR;

else

VRAMS<='1';

AHout<=ramadrswk;

ALout<=cntr2(3 downto 0);

VRAMWR<='1';

end if;

end process;

-- vblnk read

-- i/o active vrams vactive

process(Resetin,AHin,ALin,IOWR)

begin

if Resetin='0' then

vrams2<='1';

vactive<='1';

elsif AHin(3 downto 0)="1101" and ALin(3 downto 2)="00" and IOWR='0' then

vrams2<=not D0IN;

vactive<=not D1IN;

end if;

end process;

--see note 5/6

process(AHin,ALin,IORD)

begin

if AHin(3 downto 0)="1101" and ALin(3 downto 2)="00" and IORD='0' and vblnkwk='0' then

D7OUT<='0';

else

D7OUT<='Z';

end if;

end process;

rgbout<=sftrgstr(7) and hblnkwk2 and vblnkwk and vactive;

RGB_ROUT<=rgbout;

RGB_GOUT<=rgbout;

RGB_BOUT<=rgbout;

ROMadrs<=cntr3( 3 downto 1);

end rtl;

|