[新連載]CPLD入門!

〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜

いつか使うことになるだろうと思ってはいたのですが。

何を今頃になって、というようなものですが。

ようやく本気で、CPLDと四つに取り組みます。

〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜

[第62回]

●そのほかの修正箇所

前回は直していただいたVHDLプログラムの1箇所について、その部分の修正前と修正後のリストをもとに、教えていただいたevent文を書く上での留意点について説明しました。

教えていただいた基本はprocess文の中にある非同期回路は、event文の中に記述する、ということです。

その考え方で、前回と同じように直していただいたところはほかにもあります。

下は修正前です。

--cntr1 & sftrgstr

process(cntr0)

begin

if cntr0'event and cntr0='0' then

cntr1<=cntr1+"0001";

sftrgstr<=sftrgstr(6 downto 0) & '1';

end if;

if cntr1(3)='1' then

sftrgstr<=ROMDATA;

cntr1<="0000";

end if;

end process;

|

if cntr1(3)=’1’ then 〜 end if; をその前のevent文と別に記述していますが、これはevent文の中に記述するべき、ということで下のように直していただきました。

下は修正後です。

--cntr1 & sftrgstr

process(cntr0)

begin

if cntr0'event and cntr0='0' then

if cntr1="0111" then

sftrgstr<=ROMDATA;

cntr1<="0000";

else

cntr1<=cntr1+"0001";

sftrgstr<=sftrgstr(6 downto 0) & '1';

end if;

end if;

end process;

|

なるほど。

コツがちょっとわかってきました。

ですけれど。

だめだったところも出てきました。

●80字表示が出なくなってしまいました

80字表示ではうまくいっていたところが40字表示を加えたら誤動作してしまうようになった、というところから、何が原因なのか、どうすればよいのか悩んでいたところを今回助けていただいて、おかげで40字表示でムリムリ押さえていた異常動作が止まりました。

それじゃあ念のために80字のほうも確認しておこう、と思って80字表示に切り換えたところ。

なんと、画面が真っ黒です。

いや。

そんなはずは。

40字表示もうまく表示されるようになりましたし、80字のほうはもとからまともに表示していたはず。

ひょっとしてどこかにまちがっているところでもあるのか、と思ってVHDLプログラムを見直してみたのですが、特におかしいところはありません。

なぜ80字表示だと表示されなくなってしまったのか、原因がまったくわからなかったので、同期信号をオシロで確認してみましたら。

まったく何も出力されていません。

えーっ。

ということでちょいとあせって、それでプログラムを一部変更して途中の信号を逆にたどって確認してみましたところ。

なんと、クロック入力の最初のところからこけてしまっています。

最初のクロックの選択のところで、CKINをcntr0にそのまま入力しているだけのはずなのに、cntr0を出力させてオシロで確認してみたところ、ずっとH出力のままでした。

下は直していただいたままをを記述して動作確認をしてみた、最初のクロック選択のところです。

--clock select

process(CKIN)

begin

if CKIN'event and CKIN='0' then

if SW80_40='1' then

cntr0<=CKIN;

else

cntr0<=cntr0+'1';

end if;

end if;

end process;

|

なぜこんな簡単なところでこけてしまうのか、皆目見当がつかなくて、最初はまるでキツネにつままれたような気持ちだったのですが。

上のリストをじっと眺めて考えているうちに、なぜなのか、そのわけがわかりました。

そういうことだったのか!

このプログラムではelse以下の40字表示の場合はcntr0にはちゃんとCKINの1/2クロックが入ります。

しかし80字表示(SW80_40=’1’)の場合には、cntr0にはCKINは入りません。

わかってしまいましたよ!

なぜなら、このprocess文はCKINの下がりエッジのときのみ実行されます。

そのほかのとき(CKINの上がりエッジ)では実行されません。

ということは。

私はこのときcntr0にはCKINが下がった直後の値(つまり’0’)が入力されるのでは、と考えたのですが、実際には’1’が入力されていました。

多分CKINが落ちる途中の値がラッチされるのだと思います。

ということで、ここは修正前のプログラムに戻しました。

--clock select

process(CKIN)

begin

if SW80_40='1' then

cntr0<=CKIN;

elsif SW80_40='0' then

if CKIN'event and CKIN='0' then

cntr0<=cntr0+'1';

end if;

end if;

end process;

|

●前回撮り損ねた写真です

event文のからみで修正をしたところは、まだほかにもあるのですが、時間がなくなってしまいました。

ほんとうはそこのところがちょっとむつかしくてなかなかうまくクリアできずに苦労したところなのですが、それについては次回に書くことにします。

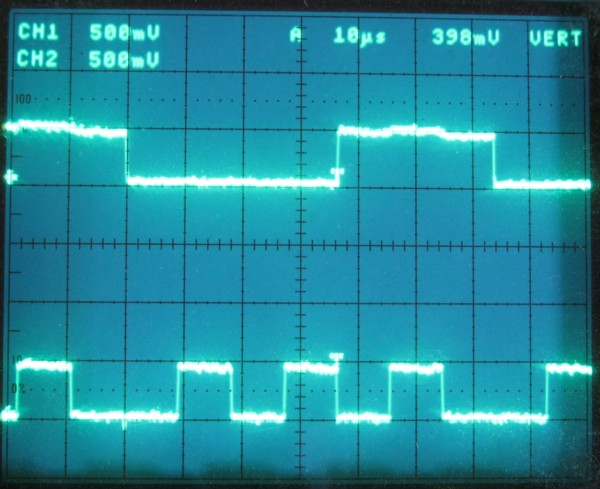

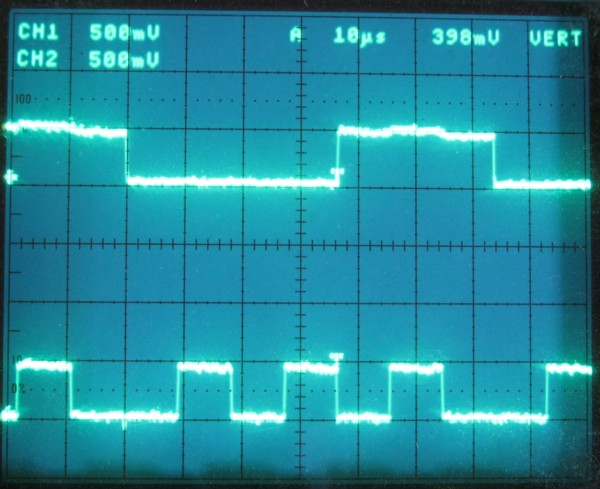

今回は最後に前回撮ったつもりで撮っていなかったcntr2の波形をあらためて撮りましたので、それを見ていただくことにします。

前回お見せした −−cntr2 の40字表示のところ(elsif SW80_40=’0’ and cntr2=”0110111” then のところ)でのcntr2の波形です。

上(CH1)がcntr2(5)で下(CH2)がcntr2(3)です。

cntr2のビット5〜ビット3が”000”から”110”までカウントアップして、おそらく”111”になったときに”000”になる様子が確認できます。

あっと。

この写真だけでは、プログラムの記述が”0110111”でよいのか、”0111000”にすべきではないのか、というあたりは判別できませんね。

そこのところがわかる写真も次回までに用意することにいたします。

CPLD入門![第62回]

2019.6.9upload

前へ

次へ

ホームページトップへ戻る