乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣

偄偮偐巊偆偙偲偵側傞偩傠偆偲巚偭偰偼偄偨偺偱偡偑丅

壗傪崱崰偵側偭偰丄偲偄偆傛偆側傕偺偱偡偑丅

傛偆傗偔杮婥偱丄俠俹俴俢偲巐偮偵庢傝慻傒傑偡丅

乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣

乵戞俋夞乶

仠幚嵺偵巊偭偰傒傑偟偨

慜夞傑偱偺偲偙傠偱偼婎杮揑側梊旛抦幆偵偮偄偰彂偄偰偒傑偟偨丅

崱夞偼偄偒側傝幚慔乮幚愴丠乯偱偡丅

僕儍僲栚婎斅偵慻傓偙偲傕偱偒傑偡偑丄係係杮傕攝慄偡傞偺偼寢峔柺搢偱偡丅

帋嶌傪寭偹偰僾儕儞僩婎斅傪嶌偭偰偟傑偄傑偟偨丅

僔儖僋偱俹俬俠倀俽俛俬俥偲儅乕僉儞僌偟偰偁傝傑偡丅

俶俢俉侽倅俁丏俆側偳偱偼俹俬俠侾俉俥侾係俲俆侽傪巊偭偨倀俽俛僀儞僞乕僼僃乕僗傪搵嵹偟偰偄傑偡丅

俹俬俠偼曋棙側偺偱偡偑丄倅俉侽側偳偺奜晹俬乛俷偲偟偰巊偍偆偲偡傞偲俠俹倀偲俹俬俠偲偺娫偺僀儞僞乕僼僃乕僗偑側偐側偐偵柺搢偱偡丅

偦偙偺晹暘傪俠俹俴俢偵抲偒姺偊偰偟傑偍偆偲偄偆傢偗偱偡丅

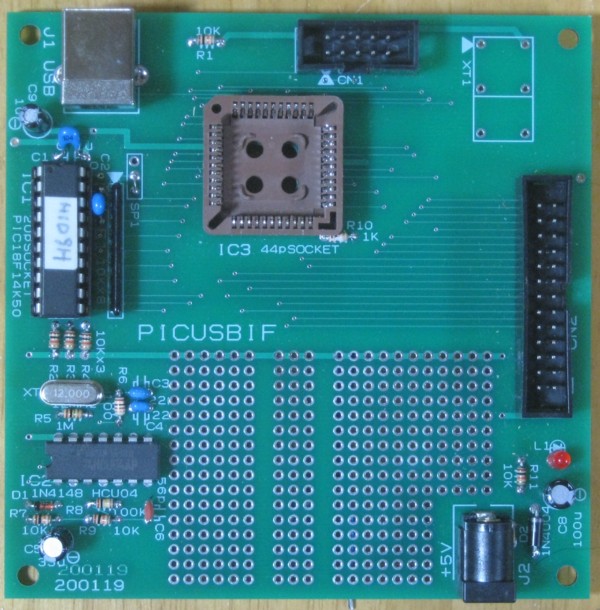

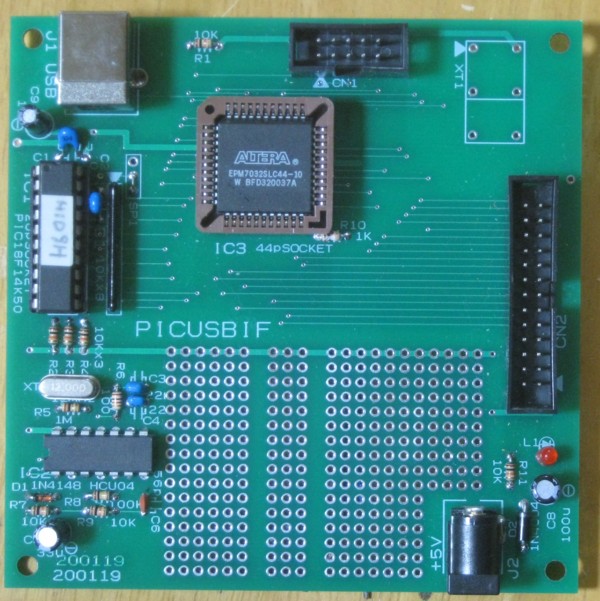

婎斅拞墰晹暘偺彮偟忋懁偵係係倫倝値俹俴俠俠僜働僢僩偑偁傝傑偡丅

俹俴俠俠僜働僢僩偵俤俹俵俈侽俁俀俽俴俠係係傪幚憰偟傑偟偨丅

偦偺忋曽偵偁傞侾侽倫倝値偺僐僱僋僞偑俰俿俙俧偱偡丅

偙偺幨恀偺傛偆偵俠俹俴俢傪僞乕僎僢僩夞楬偵幚憰偟偨傑傑夞楬僾儘僌儔儉傪俰俿俙俧傪宱桼偟偰彂偒崬傓偙偲偑偱偒傑偡丅

偲偄偆偙偲偼丄俬俠僜働僢僩傪巊傢側偔偰偠偐偵俠俹俴俢傪婎斅偵僴儞僟晅偗偟偰偟傑偭偨偁偲偐傜偱傕僾儘僌儔儉傪彂偒崬傓偙偲偑偱偒傞偺偱偡丅

偙傟偼側偐側偐偵曋棙偱偡丅

嵍懁偵偁傞偺偼俹俬俠侾俉俥侾係俲俆侽偱丄偦偺忋偵偼倀俽俛僐僱僋僞偑偁傝傑偡丅

俹俬俠侾俉俥侾係俲俆侽偺壓偵偁傞偺偼俹俬俠侾俉俥侾係俲俆侽偵侾俀俵俫倸傪嫙媼偡傞偨傔偺僋儕僗僞儖敪怳夞楬偱偡丅

塃懁偵偁傞俀俇倫倝値僐僱僋僞偼俶俢俉侽倅俁丏俆側偳偺憹愝梡俬乛俷僐僱僋僞偲摨偠抂巕攝楍偺僐僱僋僞偱偡丅

俶俢俉侽倅俁丏俆側偳偼偡偱偵俹俬俠侾俉俥侾係俲俆侽傪巊偭偨倀俽俛俬俥傪搵嵹偟偰偄傑偡偐傜丄崱夞偺夞楬傪憹愝偡傞堄枴偼偁傝傑偣傫偟丄幚嵺夞楬偑傇偮偐偭偰偟傑偄傑偡偐傜丄憹愝偡傞偙偲偼偱偒傑偣傫丅

幚偼倀俽俛俬俥傪搵嵹偟偰偄側偄倅俉侽儃乕僪乮俶俢俉侽倅俽俵乯偵愙懕偡傞偙偲傪憐掕偟偰偄傑偡丅

壓偼俶俢俉侽倅俁丏俆偺俹俬俠侾俉俥侾係俲俆侽廃曈夞楬偺偆偪崱夞嶌惉偟偨帋嶌夞楬偵憡摉偡傞晹暘偺夞楬恾偱偡丅

攋慄偱埻傫偩晹暘傪俤俹俵俈侽俁俀俽俴俠係係偵抲偒姺偊傑偟偨丅

俹俬俠侾俉俥侾係俲俆侽傪倅俉侽俠俹倀偵愙懕偡傞偨傔偵偼偙傟偩偗偺夞楬偑昁梫偵側偭偰偟傑偄傑偡丅

偦偙偺偲偙傠傪俠俹俴俢偵抲偒姺偊偰傒傑偟偨丅

杮擔偼帪娫偑側偔側偭偰偟傑偄傑偟偨丅

懕偒偼師夞偵偄偨偟傑偡丅

俠俹俴俢擖栧両乵戞俋夞乶

俀侽侾俋丏俀丏俀侽倳倫倢倧倎倓

慜傊

師傊

儂乕儉儁乕僕僩僢僾傊栠傞