(儂儞僩偼俈係俫俠丄俠俵俷俽側傫偩偗偳乧乯

乵戞俉俁夞乶

仠俹倀俽俫柦椷夞楬偺栤戣揰乮慜夞偺懕偒偱偡乯

慜夞偺廔傢傝偺偲偙傠偱丄乽俿俁偺俽俹們倢倠偲俿係偺俵俤俵倂俼偑偔偭偮偄偰偄傞偲偙傠偑栤戣乿偩偲彂偒傑偟偨丅

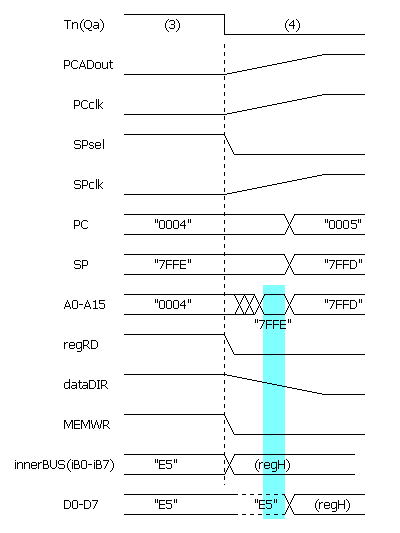

傕偆堦搙丄俹倀俽俫柦椷偺僞僀儈儞僌僠儍乕僩乮乵戞俇俋夞乶乯偱偡丅

偙偺僠儍乕僩偼奺怣崋偺抶傟傪傎偲傫偳柍帇偟偰偄傑偡丅

偦偙偱栤戣揰偑偼偭偒傝偡傞傛偆偵俿俁偲俿係偺嫬栚偺偁偨傝傪奼戝偟偰丄娭學偡傞怣崋偵傑偲傪峣偭偨僞僀儈儞僌僠儍乕僩傪昤偄偰傒傑偟偨丅

偙偺僞僀儈儞僌僠儍乕僩偼僥僗僩偵巊偭偨僾儘僌儔儉丄

侽侽侽侽丂俁侾侽侽俉侽丂丂丂俴倃俬丂俽俹丆俉侽侽侽

侽侽侽俁丂俥俆丂丂丂丂丂丂丂俹倀俽俫丂俹俽倂

侽侽侽係丂俤俆丂丂丂丂丂丂丂俹倀俽俫丂俫

侽侽侽俆丂俥侾丂丂丂丂丂丂丂俹俷俹丂俹俽倂

侽侽侽俇丂俤侾丂丂丂丂丂丂丂俹俷俹丂俫

偺偆偪偺丄

侽侽侽係丂俤俆丂丂丂丂俹倀俽俫丂俫

偺俿俁偲俿係偺嫬栚偺晹暘傪奼戝偟偰帵偟偨傕偺偱偡丅

怣崋偺偆偪偺偄偔偮偐偼丄俈係俫俠侽俁丄俈係俫俠侽俆乮偄偢傟傕僆乕僾儞僪儗僀儞僎乕僩乯偺弌椡怣崋偲僾儖傾僢僾掞峈偐傜峔惉偝傟偰偄偰丄棫偪忋偑傝偑偐側傝抶傟偰偟傑偄傑偡丅

偙偺偙偲偵偮偄偰偼乵戞俈俀夞乶偱愢柧偟傑偟偨丅

俹俠俙俢倧倳倲丄俹俠們倢倠丄俽俹們倢倠偑備傞偄岡攝偵側偭偰偄傞偺偼丄偦偺棟桼偐傜偱偡丅

倓倎倲倎俢俬俼偼壓偑傝僄僢僕偑備傞偔側偭偰偄傑偡偑丄偙傟偼儘僕僢僋夞楬偑斀揮偟偰偄傞偨傔偱丄柾幃揑側昞尰偱偡丅

俹俠乮僾儘僌儔儉僇僂儞僞乯丄俽俹乮僗僞僢僋億僀儞僞乯偼偲傕偵擖椡僋儘僢僋偺忋偑傝僄僢僕偑備傞傗偐側偨傔丄僇僂儞僩傾僢僾乮俽俹偼僇僂儞僩僟僂儞乯偡傞偺偑丄俿俁偺廔傢傝偺僞僀儈儞僌傛傝傕抶傟傑偡丅

奜晹傾僪儗僗僶僗傊偺弌椡偼丄俹俠俙俢倧倳倲偲俽俹倱倕倢偵傛偭偰丄俹俠偐傜俽俹傊愗傝姺偊傜傟傑偡偑丄椉怣崋偺僞僀儈儞僌偺僘儗偐傜丄懡暘忋偺僞僀儈儞僌僠儍乕僩偺傛偆偵丄俿係偺偼偠傔偺晹暘偱嵟弶偼俹俠偲俽俹偺弌椡偑傇偮偐傝丄偦傟偐傜俽俹偺抣偑弌椡偝傟傞偲峫偊傜傟傑偡丅

俽俹傕僇僂儞僩僟僂儞偑抶傟傞偺偱丄俽俹偺抣偑俙侾俆亅俙侽偵弌椡偝傟偼偠傔傞丄偼偠傔偺晹暘乮恾偺悈怓偺晹暘乯偱偼丄僇僂儞僩僟僂儞偡傞慜偺傾僪儗僗偑弌椡偝傟傞偲巚傢傟傑偡丅

師偼奜晹僨乕僞僶僗俢俈亅俢侽偵偮偄偰尒偰傒傑偡丅

偙偪傜偼倓倎倲倎俢俬俼偺抶傟偵傛偭偰丄僨乕僞僶僗僶僢僼傽俈係俫俠俀係俆偺岦偒偑愗傝姺傢傞偺偑抶傟傑偡丅

儊儌儕偐傜偼俿俁偺廔傢傝傑偱偼丄柦椷僐乕僪偺乭俤俆乭偑俢俈亅俢侽偵弌椡偝傟偰偄傑偡丅

俿俁偺廔傢傝偵俵俤俵倂俼偑傾僋僥傿僽偵側傞偲丄儊儌儕偐傜偺弌椡偼側偔側傝丄俢俈亅俢侽偼僴僀僀儞僺乕僟儞僗偵側傝傑偡丅

俢俈亅俢侽傕掞峈偱僾儖傾僢僾偟偰偄傑偡偑丄俴儗儀儖偺弌椡偩偭偨價僢僩偑俫儗儀儖偵側傞偺偑抶傟傞偺偼丄懠偺怣崋偺応崌偲摨偠偱偡丅

杮摉偼偙偙偱倝値値倕倰俛倀俽偐傜俫儗僕僗僞偺抣偑俢俈亅俢侽偵弌偰偔傞偼偢側偺偱偡偑丄俈係俫俠俀係俆偺岦偒偑曄傢傞偺偑抶傟傞偨傔偵丄偙偙偵僨乕僞偺嬻敀偺婜娫偑惗傑傟傑偡丅

偟偐偟偄偒側傝俢俈亅俢侽偑乭俥俥乭偵側傞偺偱偼側偔偰丄俢俈亅俢侽偺奺價僢僩偺抶傟偵傛偭偰丄偦傟傑偱儊儌儕偐傜弌椡偝傟偰偄偨乭俤俆乭偑偟偽傜偔偺娫俢俈亅俢侽偵巆偭偨忬懺偵側傝傑偡丅

儊儌儕乮俼俙俵俇俀俀俆俇僞僀僾乯偺僨乕僞僔乕僩偱偼丄僨乕僞偑儊儌儕傾僪儗僗偵彂偒崬傑傟傞僞僀儈儞僌偼俵俤俵倂俼偺棫偪忋偑傝偺僞僀儈儞僌偲偄偆偙偲偵側偭偰偄傑偡丅

偦傟側傜偄偄偺偐側偀丄偲偮偄巚偭偰偟傑偭偨偺偱偡偑丄偢偭偲挿偄娫偺宱尡偐傜乽偦傫側偼偢偼側偄偺偩偑乧乿偲偄偆媈栤偑巆偭偰偄傑偟偨丅

妋偐偵丄倂俼怣崋偺棫偪忋偑傝偺僞僀儈儞僌偱僨乕僞偑儊儌儕偵儔僢僠偝傟傞偺偱丄乽僨乕僞乿偼偦傟埲慜偵偼晄妋掕偱傕傛偄偼偢側偺偱偡偑乧丅

偟偐偟丄傾僪儗僗偵偮偄偰偼丄偦傟偲偼暿栤戣偺偼偢偱偡丅

妋偐丄僟僀僫儈僢僋俼俙俵側偳偱偼丄倂俼怣崋傪傾僋僥傿僽偵偟偰偍偄偰丄俠俽乮僠僢僾僙儗僋僩乯傪俷俶乛俷俥俥偡傞偙偲偱僨乕僞傪彂偒崬傓丄側偳偲偄偆儌乕僪偑偁偭偨傛偆偵巚偄傑偡丅

倂俼怣崋偑傾僋僥傿僽側忬懺偱傾僪儗僗傪愗傝姺偊傞偲丄懡暘愗傝姺偊慜偺儊儌儕傾僪儗僗偵偦偺偲偒偺僨乕僞偑彂偒崬傑傟偰偟傑偆丄偺偱偼側偄偐丄偲偺悇應偑側傝偨偪傑偡丅

偙偺偁偨傝傪乽偮偄偆偭偐傝乿偟偰偟傑偭偰偄傑偟偨丅

傗偼傝嵟弶偵夞楬傪峫偊偨帪揰偺傛偆偵丄俵俤俵倂俼偼僨乕僞丄傾僪儗僗偑妋掕偟偰偐傜丄傾僋僥傿僽偵偟側偗傟偽側傜側偐偭偨偺偱偡丅

仠俵俤俵倂俼夞楬傪曄峏偟傑偟偨

崱夞曄峏偟偨俵俤俵倂俼夞楬偱偡丅

峫偊曽偼乵戞俈俀夞乶偺倰倕倗倂俼夞楬偺曄峏偲摨偠偱偡丅

乵戞俈俀夞乶偺倰倕倗倂俼夞楬偐傜偺倣倕倣倂俼怣崋偼偡偱偵曄峏嵪傒偱偡偐傜丄崱夞偼偦傟偵捛壛偟偰丄俀枃栚偺婎斅偐傜偺倣倕倣倂俼怣崋偵懳偟偰們倢倠偱僎乕僩偟傑偡丅

仠俵俤俵倂俼夞楬曄峏屻偺俹倀俽俫柦椷偺僞僀儈儞僌僠儍乕僩偱偡

偦偆偄偊偽丄倰倕倗倂俼傕們倢倠偱僎乕僩偡傞傛偆偵偟偨偺偱偟偨丅

偲偄偆偙偲偼丄俹俷俹柦椷偺僞僀儈儞僌僠儍乕僩傕曄傢傝傑偡丅

仠倰倕倗倂俼夞楬曄峏屻偺俹俷俹柦椷偺僞僀儈儞僌僠儍乕僩偱偡

偡偱偵愢柧偟偨偙偺傎偐偺柦椷偺僞僀儈儞僌僠儍乕僩偵偮偄偰傕丄俵俤俵倂俼丄倰倕倗倂俼偺怣崋偺僞僀儈儞僌偼慡晹丄忋偺俹倀俽俫柦椷丄俹俷俹柦椷偺僞僀儈儞僌僠儍乕僩偲摨偠僞僀儈儞僌偵側傝傑偡偑丄偄偪偄偪曄峏偡傞偺傕庤娫偱偡偺偱丄偦偺傑傑偵偟偰偍偒傑偡丅

俀侽侽俉丏俋丏俁侽倳倫倢倧倎倓

慜傊

師傊

儂乕儉儁乕僕僩僢僾傊栠傞