俹俬俠俛俙俽俬俠僐儞僷僀儔

乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣

傑傞偱僀儞僞僾儕僞丅偱傕僐儞僷僀儔偱偡丅挻僇儞僞儞挻僔儞僾儖偱偡丅

乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣

乵戞俀侾俈夞乶

仠俹俬俠侾俇俥俇俀俈乮侾俀乯倢倧倗倝倎値倎偱夝愅乮俆乯

偙偺偲偙傠偢偭偲俹俬俠侾俇俥俇俀俈偺俤俼俙俽俤栤戣偵偮偄偰彂偄偰偄傑偡丅

偦偺栤戣偼偡偱偵夝寛嵪傒側偺偱偡偑寢壥偵帄傞崿柪偺夁掱傪旛朰榐偲偟偰巆偟偨偄偲巚偭偰偁傟偙傟柪偄偵柪偭偨偙偲側偳傪彂偄偰偄傑偡丅

慜夞偼偨傑偨傑侾侾擭傕慜偵彂偄偨婰帠傪撉傒捈偟偰傒偰丄悘暘偡偛偄偙偲傪傗偭偰偄偨偺偩側偁偲帺暘偺偙偲偱偁傝側偑傜偪傚偄偲姶摦偟偰偟傑偄傑偟偨丅

偦偺偙傠偵斾傋傑偡偲偙偺偲偙傠偺婰帠偺撪梕側偳偼偪傚偭偲敄偭傌傜偄偺偱偼側偄偐偲巚偭偰偟傑偄傑偡丅

偮偄柺搢偵側偭偰尵梩偩偗偱敳偗傛偆偲偟偰偄傞偺偱偼側偄偐丅

斀徣偱偡丅

弶怱偵栠偭偰側傞傋偔偟偮偙偔嬶懱揑偵彂偔傛偆偵偟偨偄偲巚偄傑偡丅

側傫偨偭偰旛朰榐側偺偱偁傝傑偡偐傜丅

偟偐偟丅

偁偁丅

帪娫偑梸偟偄丅

慜夞偼壓偺傛偆偵彂偒傑偟偨丅

乽

徻嵶偼徣偒傑偡偑俶俢俉侽倅俁丏俆傪巊偭偰俹俬俠俲俬俿嘦偐傜弌椡偝傟傞嵟弶偺俹俧俠僷儖僗傪撉傫偱僗僞乕僩偡傞僾儘僌儔儉傪嶌偭偰丄嵟弶偺俁侽倣倱偺婜娫偼柍帇偟偨偁偲師偵俹俧俠僷儖僗偑弌尰偡傞傑偱偺帪娫傪俬俶柦椷偲儗僕僗僞偺僇僂儞僩倀俹傪慻傒崌傢偣傞偙偲偱應掕偟傑偟偨丅

偦偺娫偵僇僂儞僩偝傟偨儗僕僗僞乮俫丄俴丄俛丄俠傪偮側偄偩俁俀價僢僩僇僂儞僞乯偺抣傪撉傓偙偲偱偦偺偍傛偦偺宱夁帪娫傪應掕偟偰傒傑偟偨丅

寢壥偼嵟弶偺僨僶僀僗俬俢偺庢摼偐傜師偺僐儅儞僪傑偱偺娫偵

乿

乮忋婰侾俈侽倣倱偺偲偙傠偺掶惓偵偮偄偰偼崱夞偺壓偺傎偆偵彂偄偰偁傝傑偡乯

偣偭偐偔俶俢俉侽倅俁丏俆傪巊偭偨偺偱偁傝傑偡偐傜丄偦偙偺偲偙傠傪偳偺傛偆偵偟偨偺偐撉幰條偺嶲峫偵傕側傝傑偡傛偆偵彂偔傋偒偱偁傝傑偟偨丅

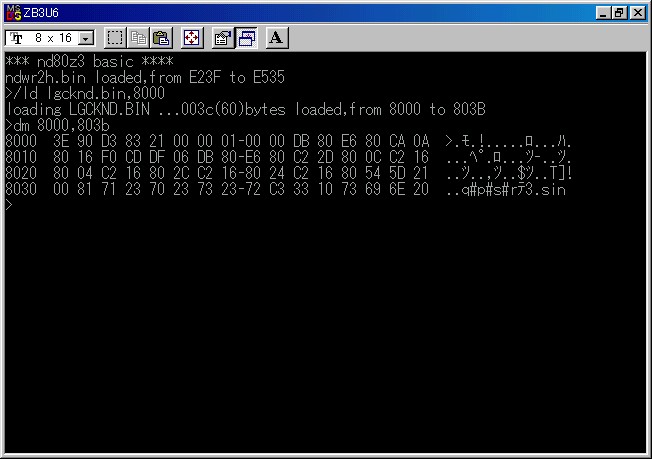

傑偢偼尰応幨恀偱偡丅

嵍偼俹俬俠俲俬俿嘦偱偡丅

塃偼俶俢俉侽倅俁丏俆乮帋嶌婎斅乯偱偡丅

崱偼朸仜崙偺婎斅儊乕僇乕偵敪拲偟偰偍傝傑偡偺偱帋嶌偱傕偟偭偐傝儗僕僗僩晅偒偱偡丅

偲偄偆傛傝彮検偺敪拲偼慡偰帋嶌埖偄乮倫倰倧倲倧倲倷倫倕乯偱偡丅

俶俢俉侽倅俁丏俆偺帋嶌婎斅傪嶌偭偨摉帪偼崙撪儊乕僇乕偵敪拲偟偰偄傑偟偨丅

儗僕僗僩晅偒偩偲偦偺暘偺惢斉戙偑偐偐傝傑偡偺偱帋嶌偼傕偭傁傜儗僕僗僩側偟偱敪拲偟偨傕偺偱偡丅

挷傋偰傒傑偟偨傜俀侽侾俀擭壞偺惢憿婎斅偱偟偨丅

側傫偲侾俀擭傕慜偺婎斅偱偡丅

偦傟偑崱傕尰栶偱偡丅

偪傚偄偲帺夋帺巀偱偡偗傟偳側偐側偐偺傕偺偱偁傝傑偟傚偆丅

偦傟偱榖傪栠偟傑偟偰丅

傗偭偰偄傞偙偲偼娙扨側偙偲偱偡丅

俶俢俉侽倅俁丏俆偺俬乛俷乮俉俀俠俆俆乯偺俹俙俈乮偳偺億乕僩偱傕傛偄偺偱偡偗傟偳乯傪俹俬俠俲俬俿嘦偺俹俧俠抂巕偵偮側偓俧俶俢傪愙懕偟傑偡丅

俹俬俠侾俇俥俇俀俈偼俀俉倫倝値僜働僢僩偵幚憰偟傑偡偑嬻偄偰偄傞係侽倫倝値僜働僢僩偺俁俋倫倝値偵傕俹俧俠偑攝慄偟偰偁傝傑偡偐傜崱夞偼偦傟傪巊偄傑偡丅

偁偭偲丅

朰傟傞偲偙傠偱偟偨丅

忋偺幨恀偺傛偆偵愙懕偟偰應掕傪奐巒偟偨偺偱偡偑抣偑庢傟傑偣傫丅

妋擣偟偰傒偨偲偙傠俹俙俈偺擖椡偑晜偒忋偑偭偰拞娫揹埵偵側偭偰偄傑偟偨丅

彂偒崬傒奐巒慜偼俹俬俠俲俬俿嘦偺俹俧俠弌椡偼僴僀僀儞僺乕僟儞僗偱偼偁傝傑偣傫偑弌椡掞峈抣偑偐側傝崅偄傛偆偱偡丅

偙傟偱偼應掕偱偒傑偣傫偐傜俶俢俉侽倅俁丏俆偺俉俀俠俆俆偺擖椡夞楬偵偮偗偰偁傞僾儖傾僢僾掞峈乮侾侽俲兌乯傪奜偟傑偟偨丅

偙偆偄偆応崌偵偼僾儖傾僢僾掞峈偼柍偄傎偆偑傛偄偱偡偹偊丅

僴乕僪偲偟偰偼偦傟偱弨旛俷俲偱偡丅

師偼僾儘僌儔儉偱偡丅

娙扨側僾儘僌儔儉偱偡偐傜俶俢俉侽倅俁丏俆偺傾僪儗僗俉侽侽侽乣偵捈愙儅僔儞岅僐乕僪傪懪偪崬傫偱嶌傝傑偟偨丅

壓偺夋柺偼偦傟傪僼傽僀儖偲偟偰曐懚偟偨傕偺傪嵞儘乕僪偟偰偄傑偡丅

偱傕偙傟偠傖偁壗傪傗偭偰偄傞偺偐傢偐傝傑偣傫偹丅

俶俢俉侽倅俁丏俆偺晬懏俠俢俼俷俵偵偼曋棙側僣乕儖偑擖偭偰偄傞偺偱偡丅

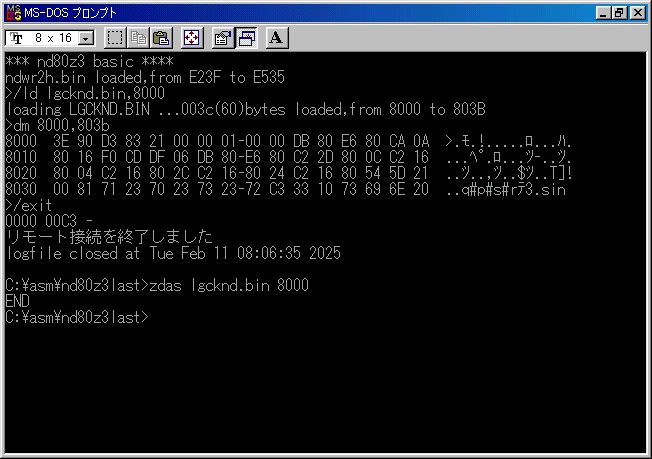

堦扷倅俛俁俛俙俽俬俠傪廔椆偟偰俵俽俢俷俽僾儘儞僾僩乮僐儅儞僪僾儘儞僾僩乯偵栠傝傑偡丅

偙偺夋柺偼倂倝値倓倧倵倱俋俉俽俤偱偡丅

偙偆偄偆嶌嬈偼倂倝値倓倧倵倱俈側偳傛傝傕妝側偺偱偄傑偩偵倂倝値倓倧倵倱俋俉俽俤偼庤曻偣傑偣傫丅

倅俢俙俽僾儘僌儔儉偱俴俧俠俲俶俢丏俛俬俶傪媡傾僙儞僽儖偟傑偟偨丅

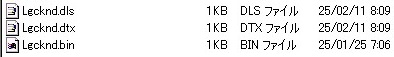

俴俧俠俲俶俢丏俢俴俽偲俴俧俠俲俶俢丏俢俿倃偑嶌惉偝傟傑偟偨丅

俴俧俠俲俶俢丏俢俴俽傪奐偄偰傒傑偟偨丅

拞恎偼俿倃俿側偺偱儊儌挔傗俿倕倰倎俹倎倓側偳偱奐偗傑偡丅

偆傑偔奐偗側偄偲偒偼奼挘巕傪俿倃俿偵曄峏偟偰偟傑偊偽奐偗傞傛偆偵側傝傑偡丅