仠俠俹俴俢斉俠俼俿俬俥

偙偺偲偙傠俠俹俴俢斉倁俧俙俬俥偵偮偄偰彂偄偰偒傑偟偨丅

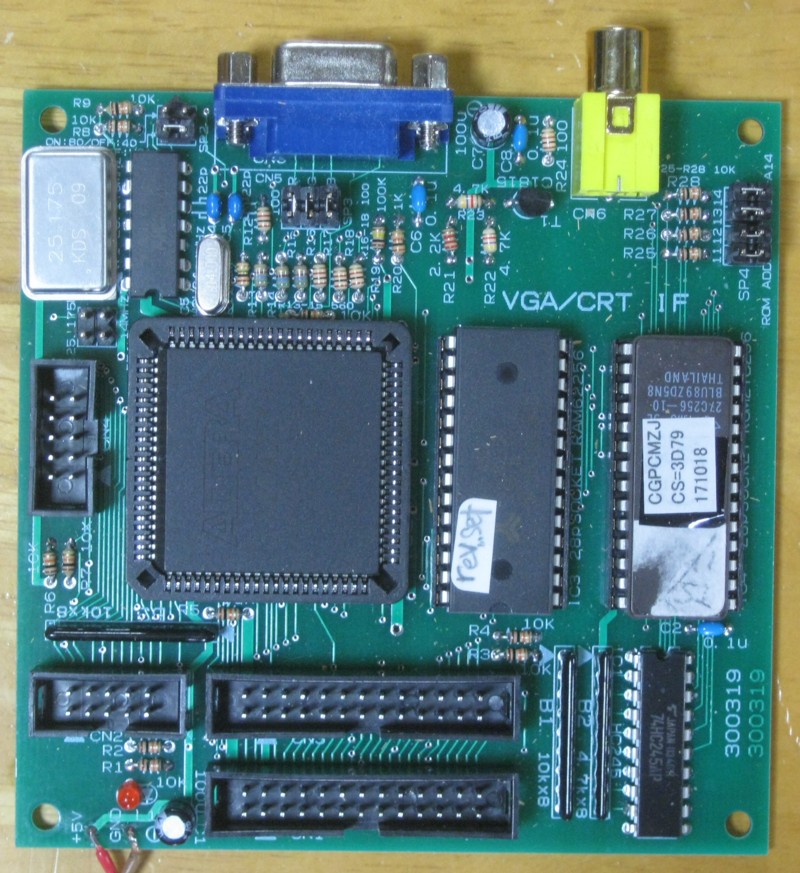

俠俹俴俢斉倁俧俙俬俥惢嶌偺嶲峫偵偟偨俈係俫俠傪巊偭偨俠俼俿乛倁俧俙俬俥儃乕僪偼偦偺柤偺捠傝俠俼俿俬俥偲倁俧俙俬俥偺椉曽偺夞楬傪搵嵹偟偰偄傑偡丅

偦偺夞楬偼憡摉偵暋嶨側夞楬側偺偱丄偦傟傪偦偺傑傑偄偒側傝俠俹俴俢壔偟傛偆偲偡傞偲丄摉慠倁俫俢俴僾儘僌儔儉傕暋嶨側傕偺偵側偭偰偟傑偄傑偡丅

摿偵僾儘僌儔儉偺応崌偵偼丄偁偲偐傜偱傕斾妑揑妝偵捛壛曄峏偡傞偙偲偑壜擻側偺偱乮偦傟偑僜僼僩僂僃傾偲偄傢傟傞強埲偱偡乯丄傑偢偼倁俧俙俬俥夞楬偺傒偺俠俹俴俢壔傪帋傒傑偟偨丅

傑偢偼惢嶌偺斖埻傪倁俧俙俬俥偺傒偵偟傏偭偨偺偼丄忋婰偺捠傝偄偒側傝暋嶨側倁俫俢俴僾儘僌儔儉傪彂偙偆偲偡傞嬸傪旔偗傞偨傔偱傕偁傝傑偟偨偑丄偦傕偦傕倁俧俙俬俥偲俠俼俿俬俥偺椉曽傪偁傢偣偨倁俫俢俴僾儘僌儔儉偑俤俹俵俈侾俀俉俽俴俠俉係偵廂傑傞偐偳偆偐媈栤偩偭偨偐傜偱傕偁傝傑偟偨丅

幚嵺偵倁俧俙俬俥偺倁俫俢俴僾儘僌儔儉傪彂偄偨偲偙傠丄乵戞係俋夞乶偵彂偒傑偟偨捠傝丄侾俀俉屄偁傞倣倎們倰倧們倕倢倢偺偆偪俇俈屄乮俆俀亾乯傪巊梡偟偨偩偗偱嵪傒傑偟偨丅

偦傟側傜丅

偦偙偵俠俼俿俬俥傪捛壛偟偰傕丄偍偦傜偔廫暘廂傑傝偦偆偱偡丅

偲偄偆偙偲偱丄崱傑偱偺俠俹俴俢斉倁俧俙俬俥夞楬偵俠俼俿俬俥夞楬傪捛壛偟傑偟偨丅

壓偑夞楬恾偱偡丅

俠俼俿俬俥傪捛壛偡傞慜偺夞楬恾偼乵戞係俇夞乶偵偁傝傑偡丅

僾儕儞僩婎斅傕嶌傝捈偟傑偟偨丅

倁俧俙俬俥偺傒偺婎斅乮乵戞係俈夞乶乯偵斾傋傞偲偐側傝晹昳揰悢偑憹偊傑偟偨丅

愢柧偺搑拞偱偡偑杮擔偼帪娫偑偁傝傑偣傫丅

懕偒偼師夞偵偡傞偙偲偵偄偨偟傑偡丅

俠俹俴俢擖栧両乵戞俆俀夞乶

俀侽侾俋丏俆丏俀係倳倫倢倧倎倓

慜傊

師傊

儂乕儉儁乕僕僩僢僾傊栠傞